台台积电(TSMC)董事长魏哲家在上周的法说会上宣布,公司正在积极研发扇出型面板级封装技术(Fan-Out Panel-Level Packaging,简称 FOPLP),并计划于 2027 年能进入量产,有望为半导体封装在性能和产能方面取得显著提升。

台积电先进封装技术,严重供不应求

有在关心最近半导体消息的读者,一定知道最近 CoWoS 封装技术产能极度匮乏的消息。本周就传出,今年 6 月炫风来台的辉达创办人黄仁勋,亲自登门拜访台积电,要求「台积电能在厂外设立辉达独家专属的 CoWoS 产线」的需求,但遭到台积电高层强硬回绝:

辉达要出钱吗?要不要台积电在厂区外也设专门给辉达的晶圆生产线?

科技业人士表示台积电会拒绝并非没有道理,因为一旦答应辉达,接下来苹果、超微和高通等大客户都会要求比照办理,后果难以收拾,且目前台积电 CoWoS 产能严重供不应求、量产难度高,台积电历经多年才克服良率问题,专利也掌握在台积电自己手中。

FOPLP 是什么?和 CoWoS 差异?

先进封装简单来说,就是将不同种类的晶片(逻辑晶片、记忆体、射频晶片…),透过封装及堆叠技术整合在一起,以提升晶片性能、缩小尺寸、减少功耗。

现在许多高端 AI 晶片都已采用 CoWoS 技术,并主要使用台积电的 2.5D CoWoS 封装制程,包括辉达的 H100、A100 GPU ,先前外资就曾指出,辉达是目前台积电 2.5D CoWoS 产能的最大客户,占比达 40% ~ 50%。

由于台积电 CoWos 产能吃紧成为辉达去年 AI 晶片生产的一大瓶颈,辉达先前在投资者会议上也曾表示,已在 CoWoS 的关键制程已开发并认证其他供应商产能,预期未来数季晶片供应可逐步上升。

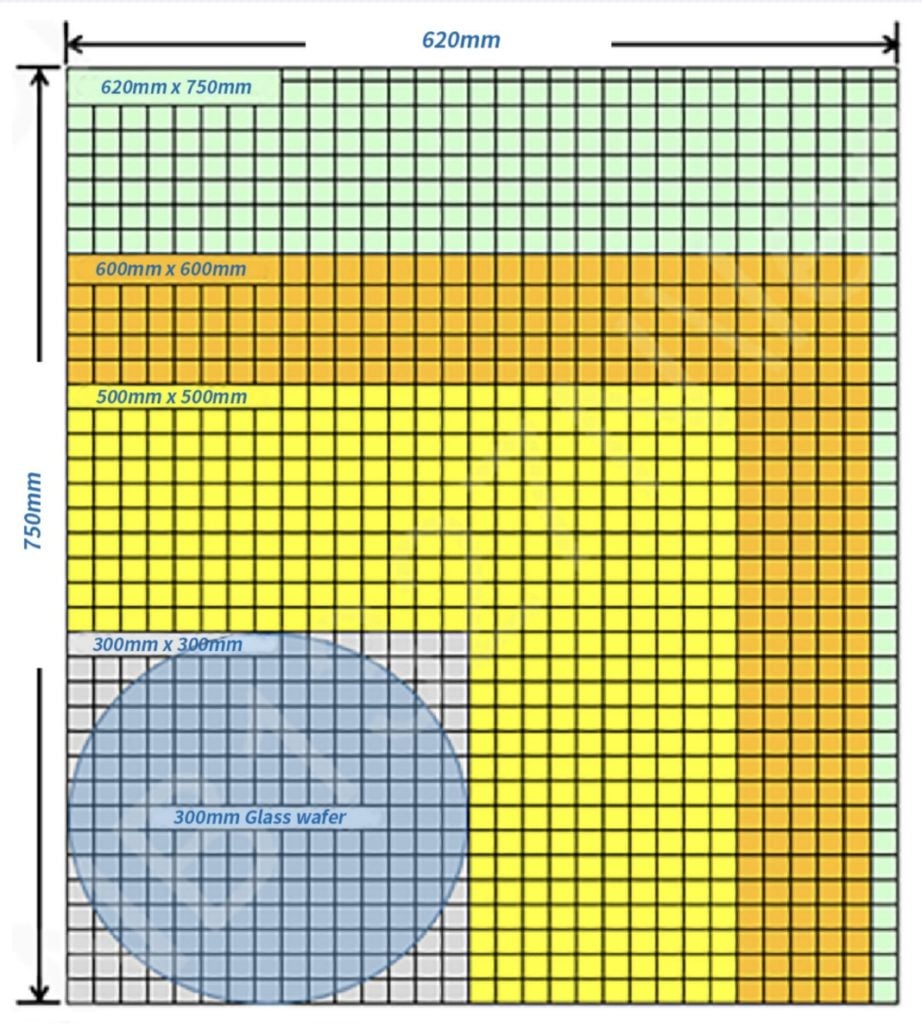

而作为更先进技术的「FOPLP」之所以近期备受关注的原因,因为其利用方形基板来进行 IC 封装,与传统圆形基板相比能更高效地利用空间、提高生产效率。

FOPLP 的优势

FOPLP 技术的核心优势在于其高效的空间利用率,利用方形基板进行 IC 封装,在同等面积下,可以摆放更多的晶片,最高可达 7 倍之多,从而提高生产效率,减少材料浪费,并降低成本。

这对于半导体行业来说是一项重要的技术进步,能显著提升晶片的性能和能效。此外,FOPLP 技术还具有良好的散热性能和低电阻特性,这些特点使其非常适合应用于高性能计算和电源管理等领域。

台积电预计,FOPLP 技术将在未来三年内逐步成熟,并在 2027 年实现大规模化量产。

FOPLP 面临的挑战

尽管 FOPLP 技术具备显著的优势,但仍需克服一些挑战,如面板翘曲、均匀性和良率问题,这些问题主要来自于制造工艺的复杂性和高精度要求。

然而,随著技术的不断进步和企业的持续努力,这些挑战有望在未来得到解决。辉达(NVIDIA)也计划将 FOPLP 技术提前至 2025 年上线,显示出该技术巨大的市场潜力、以及 AI 晶片的需求。

FOPLP 概念股有哪些?

除了台积电之外,还有以下几间大厂受益,激励股价:

- 日月光 (ASE Technology Holding Co.):日月光在封装测试领域拥有强大的实力,是 FOPLP 技术的重要参与者。

- 群创 (Innolux Corporation):群创早在几年前就布局了 FOPLP 技术,其股价也因此大涨。

- 东捷 (Tong Hsing Electronic Industries Ltd.):东捷相继推出对应面板级扇出型封装的机台,并陆续有出货实绩。

- 晶彩科 (GIS Holdings):晶彩科受惠于 MicroLED 和面板级封装 FOPLP 等设备出货,股价受激励。

- 鑫科 (Xintec Inc.):中钢旗下的鑫科切入面板级扇出封装 (FOPLP) 引发市场关注,公司表示,下半年到明年出货可望倍增,加上半导体靶材、贵金属等需求转好,以及并购中钢精材效益显现,到明年都乐观以对。。